Code composer studio for mac code#

During the ISR, the following actions take place: the 32-bit input sample (denoted by x in the diagram) is read from the McBSP, and sent into the sample processing algorithm that computes the correspondingĢ 1 TMS320C6713 DSK AND CODE COMPOSER STUDIO 8 32-bit output word (denoted by y), which is then written back into a 32-bit transmit-register of the McBSP, from where it is transferred to the codec and reconstructed into analog format, and finally the ISR returns from interrupt, and the processor begins waiting for the next interrupt, which will come at the next sampling instant. Upon receiving the interrupt, the processor executes an interrupt service routine (ISR) that implements a desired sample processing algorithm programmed with the CCS (e.g., filtering, audio effects, etc.).

Code composer studio for mac serial#

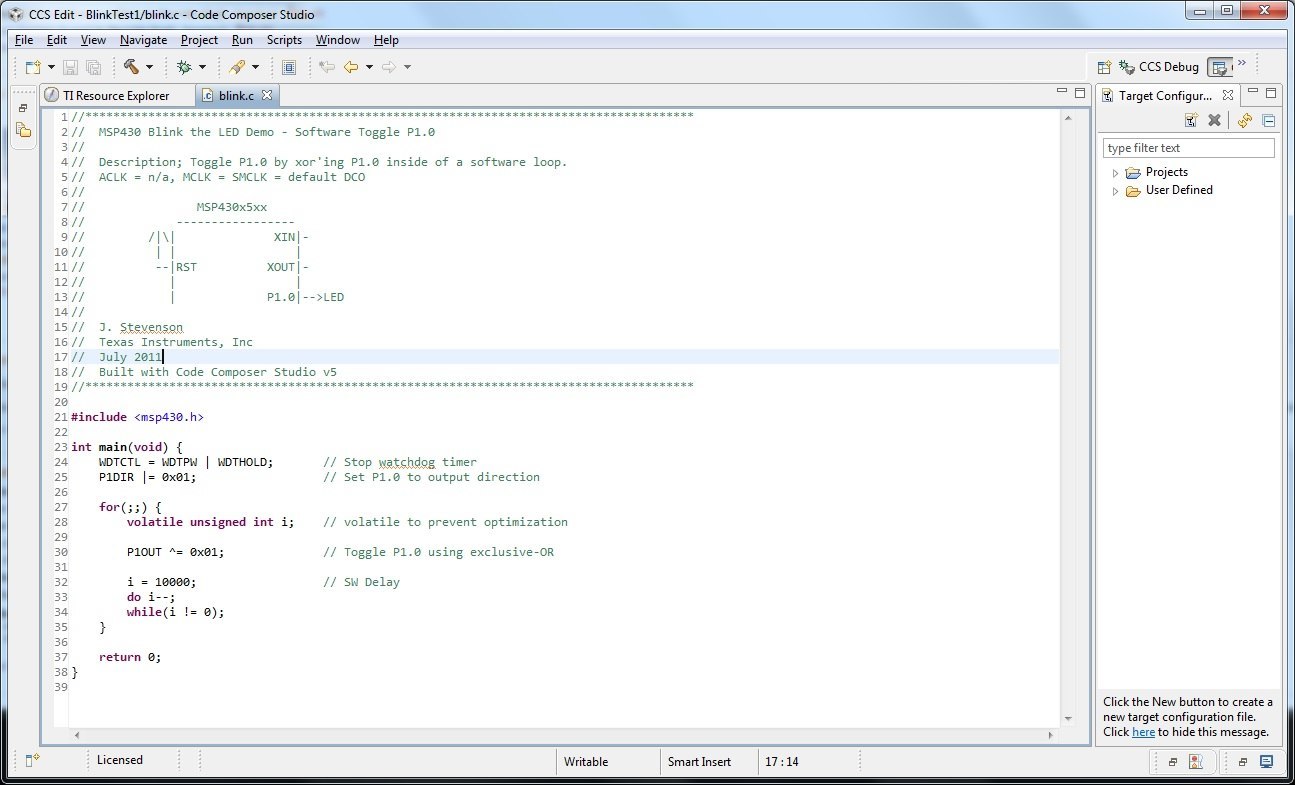

At each sampling instant, the codec combines the two 16-bit left/right samples into a single 32-bit unsigned integer word (an unsigned int, oruint32 data type in C), and ships it over to a 32-bit receiveregister of the multichannel buffered serial port (McBSP) of the C6713 processor, and then issues an interrupt to the processor. The codec actually samples the audio input in stereo, that is, it collects two samples for the left and right channels. Each collected sample is converted to a 16-bit two s complement integer (a short data type in C). The AIC23 codec is configured (through CCS) to operate at one of the above sampling rates f s. Processing is interrupt-driven at the sampling rate f s, as explained below. The following block diagram depicts the overall operations involved in all of the hardware experiments in the DSP lab. In addition to facilitating all programming aspects of the C6713 DSP, the CCS can also read signals stored on the DSP s memory, or the SDRAM, and plot them in the time or frequency domains. The CCS communicates with the DSK via a USB connection to a PC. All features of the DSK are managed by the CCS, which is a complete integrated development environment (IDE) that includes an optimizing C/C++ compiler, assembler, linker, debugger, and program loader. The DSK also has four user-programmable DIP switches and four LEDs that can be used to control and monitor programs running on the DSP. The DAC part is similarly implemented as a multi-bit second-order noise-shaping delta-sigma converter whose oversampling interpolation filters act as almost ideal reconstruction filters with the Nyquist interval as their passband. The corresponding oversampling decimation filters act as anti-aliasing prefilters that limit the spectrum of the input analog signals effectively to the Nyquist interval. 2& 12 of for the theory of such converters) that allows a variety of oversampling ratios that can realize the above choices of f s. The AIC23 codec can be programmed to sample audio inputs at the following sampling rates: f s = 8, 16, 24, 32, 44.1, 48, 96 khz The ADC part of the codec is implemented as a multi-bit third-order noise-shaping delta-sigma converter (see Ch. There are four 3.5 mm audio jacks for microphone and stereo line input, and speaker and head-phone outputs. It has an on-board 16-bit audio stereo codec (the Texas Instruments AIC23B) that serves both as an A/D and a D/A converter. The DSK board includes a 16MB SDRAM memory and a 512KB Flash ROM. The C6713 processor has 256KB of internal memory, and can potentially address 4GB of external memory. During each clock cycle, up to eight instructions can be carried out in parallel, achieving up to = 1800 million instructions per second (MIPS).

The basic clock cycle instruction time is 1/(225 MHz)= 4.44 nanoseconds. Introduction The hardware experiments in the DSP lab are carried out on the Texas Instruments TMS320C6713 DSP Starter Kit (DSK), based on the TMS320C6713 floating point DSP running at 225 MHz.

1 7 Lab 1 TMS320C6713 DSK and Code Composer Studio 1.1.

0 kommentar(er)

0 kommentar(er)